# Crosstalk Peak Overshoot Analysis of VLSI Interconnects

# <sup>1</sup>C. Venkataiah, <sup>2</sup>D. Rajesh Setty, <sup>3</sup>N. Ramanjaneyulu, <sup>4</sup>Y. Mallikarjuna Rao

<sup>1,2,3</sup>Rajeev Gandhi Memorial College of Engineering and Technology, Nandyal, India <sup>4</sup>Santhiram Engineering College, Nandyal, Andhra Pradesh-518501, India

Abstract: As technology extended from deep sub-micron technology to nanometer regimes, the conventional copper (Cu) wire will not be able to continue. Now a substitute approaches such as Carbon Nano Tube (CNT) interconnects have been suggested to ignore the problems associated with global interconnects. Hence in this work, crosstalk analysis of Complementary metal oxide semiconductor (CMOS) buffer-driven of different interconnects have been analyzed for peak overshoot and overshoot width of Cu and CNTs for 16nm technology. For analyzing peak overshoot, the interconnect lengths are varied from 100um to 500um in 16 technology node for Cu, single walled carbon nanotube (SWCNT) and multi-walled carbon nanotube (MWCNT). The values of the peak overshoot and overshoot width changes, as the interconnect length increases, the peak overshoot and width is going to be increases. As Compared to Cu, SWCNT and MWCNT, the peak overshoot and width for SWCNT is lesser than copper and MWCNT. The MWCNT interconnect is less than that of conventional Copper interconnects.

Keywords: CMOS inverter, Crosstalk, Interconnect, Power dissipation.

#### **1 INTRODUCTION**

As VLSI advancements into sub-micron interconnect wire will play an important role in the overall delay performance and analysis of power consumption of better chips. Interconnect transmission delay will have more impact on device delay and make a performance bottleneck [1-5]. More interconnecting wires and the amount of resistance and resources that may require a lot to drive the wires may also increase. Hence, increasing the amount of power dissipation in integrated circuits. Improvement in technology or scaling leads to provide a significant increase in parasitic interconnects wires [6-12]. The inductive effect and capacitive coupling effect give interconnect wire coupling crosstalk significance and cause many signal integrity problems. Hence, interconnect wire downscaling is thus careful to be the real contest to CMOS scaling [12-19].

Low power requirement is prominent for today all electronics equipment, but it holds many challenges and design issues [20]. Avoid crosstalk noise and decreasing transition delays is a major challenge in a scaled device as technology nodes decrease. Ultralow power circuit design has received a wide attention due to the fast growth and prominence of portable battery-operated devices with stringent power constraint. Sub-threshold circuit operation satisfies the ultra-low power requirement to some extent, but it holds challenging design issues [20-22]. Of these, the increased crosstalk and delay have become serious challenges, particularly for sub threshold interconnects as integration density increases with every scaled technology node.

#### **2** VLSI INTERCONNECTS

In the past, Copper (Cu) interconnects replaced aluminium interconnects due to the low resistance to electron migration was much higher in copper when compared with aluminium, now copper interconnects are going through similar problems due to the growing resistivity. As the processing technology is approaching the sub nano-meter regime delay is becoming serious concern. From the report of International Technology Roadmap for Semiconductors (ITRS), find that copper resistivity for future technologies is increasing at a very large rate. Therefore, the better alternative to copper as the size shrinking is done is carbon nanotube (CNT). CNTs are the most promising materials used to work at high speed and low power interconnects due to ballistic transport between the ends of interconnects. These are categorized as single-walled Carbon Nanotubes (SWCNTs) and multi-walled Carbon Nanotubes (MWCNTs). There are other techniques that have been proposed to reduce signal transition delays and crosstalk issues such as buffer or repeater insertion techniques, but they have not reported for CNT based interconnects [7,8]. So, this work is extended from deep sub-micron technology to nanometre regimes, under this conventional Cu wire will not be able to continue. Hence substitute approaches such as Carbon Nano Tube (CNT) interconnects have been suggested to ignore the problems associated with global interconnects. In this work, analyzed the carbon nanotube based interconnects by varying the length.

#### **3 RESULT ANALYSIS**

The HSPICE simulator is used to simulate interconnects and their corresponding results are obtained by using the Cosmos Scope. Some of the resultant wave forms are shown below. These wave forms reflect the disadvantages of crosstalk in interconnects.

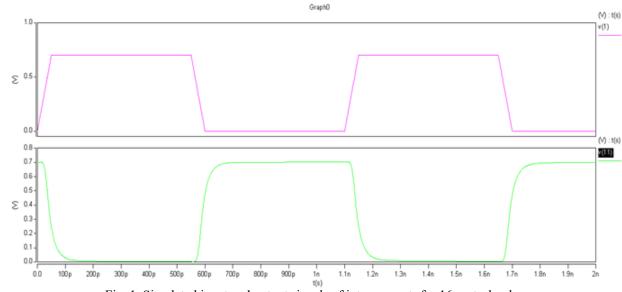

Fig. 1. Simulated input and output signals of interconnects for 16nm technology

The Fig. 1 illustrates input and output signals of interconnect for 16nm technology, the Fig. 1 has two signals in which above one is input signal and the below one is output signal. The output signal has some delay compared to that of the input signal, this delay due to the presence of components in interconnects. The value of delay can be directly found in the .mto file of the Hspui.

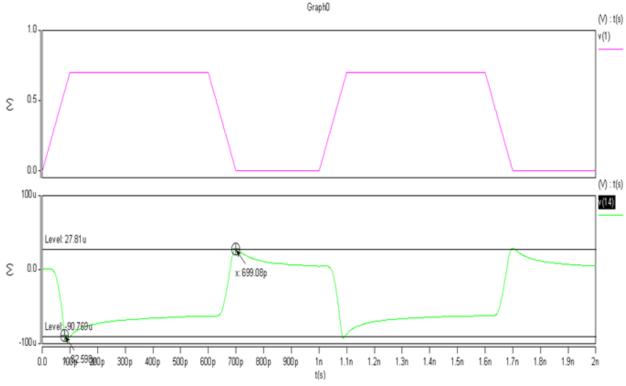

Fig. 2. Peak Overshoot and Undershoot due to crosstalk effect.

The Fig. 2 illustrates the peak overshoot and undershoot in interconnects due to the effect of the crosstalk. In Fig. 2, the top one indicates the input signal and the below one is the output signal, in the output signal it consists of the peak overshoot and undershoot. The value of those parameters is calculated by using at Y measurement in the Cosmos Scope.

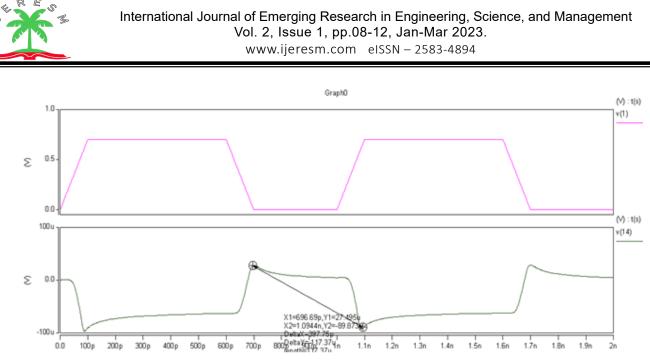

Fig. 3. Overshoot pulse width due to Crosstalk delay

The Fig. 3 illustrates the overshoot pulse width in interconnects due to the effect of the crosstalk. In Fig. 3, top one indicates the input signal and the below one is the output signal, in the output signal it consists of the overshoot pulse width. The value of the overshoot pulse width is calculated by using at Point to Point measurement in the Cosmos Scope. In this work, analyzed the peak overshoot and overshoot width for different technologies by varying the length for the Cu and CNTs.

| Table | 1 Peak  | overshoot | (11 volte) | ) in | 16nm | Tech | for co | oupled lines. |  |

|-------|---------|-----------|------------|------|------|------|--------|---------------|--|

| Table | г. геак | overshoot | (µ vons    | ) Ш  | romm | rech | 101 00 | Jupieu mies.  |  |

| Length (µ m) | SWCNT | MWCNT | COPPER |

|--------------|-------|-------|--------|

| 100          | 0.48  | 0.5   | 64.77  |

| 200          | 0.412 | 1.32  | 72     |

| 300          | 0.277 | 1.458 | 73     |

| 400          | 0.169 | 3.092 | 74.5   |

| 500          | 0.164 | 4.49  | 75     |

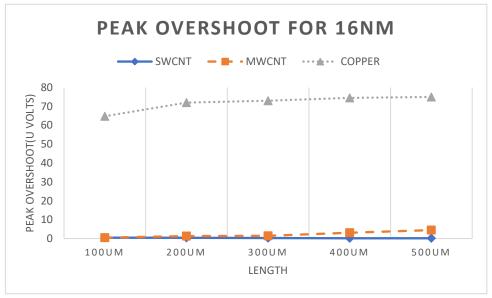

Fig. 4. Peak overshoot (µ volts) in 16nm Technology for coupled lines.

The above table 1 and fig. 4 describes the peak overshoot for different lengths of 16nm technology, as the length increases the peak overshoot is also going to be increases. Comparing to Cu, SWCNT and MWCNT the peak overshoot for SWCNT is less than that of MWCNT and MWCNT having less than that of Cu.

#### IJERESM@2023

| Length (µ m) | SWCNT   | MWCNT   | COPPER |

|--------------|---------|---------|--------|

| 100          | 0.1078  | 0.10933 | 1.5967 |

| 200          | 0.11269 | 0.11166 | 1.66   |

| 300          | 0.1156  | 0.18511 | 1.761  |

| 400          | 0.119   | 0.2825  | 1.938  |

| 500          | 0.125   | 0.2955  | 2.984  |

| Table 2. Overshoot width ( $\mu$ volts) in 16nm Technology for coupled lines. |                              |           |               |            |                    |

|-------------------------------------------------------------------------------|------------------------------|-----------|---------------|------------|--------------------|

| Table 2. Overshool which the volts $The Tohn Technology for complete thes.$   | Table ? Overshoot width (    | 'u volte' | ) in 16nm     | Technology | for coupled lines  |

|                                                                               | 1a016 2.0 versitoot within ( | µ vons    | ) III 10IIIII | rechnology | tor coupled lines. |

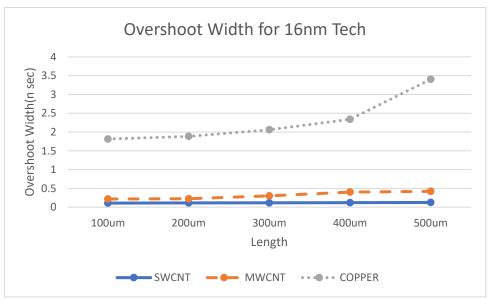

Fig. 5. Overshoot width (µvolts) in 16nm Technology for coupled lines.

The above Table 2 and Fig. 5 describes the overshoot width for different lengths of 16nm technologies, as the length increases the Overshoot width is also going to be increases. Comparing to Cu, SWCNT and MWCNT the overshoot width for SWCNT is less than that of MWCNT and MWCNT having less than the conventional copper interconnect.

## 4 CONCLUSIONS

In this work, crosstalk analysis of CMOS buffer-driven of different interconnects have been analyzed for peak overshoot of Cu and CNTs for 16nm technology. For analyzing peak overshoot and overshoot has been varied the interconnect lengths from 100um to 500um in 16nm technology node for Cu, SWCNT and MWCNT. The values of the peak overshoot and overshoot width changes, as the interconnect length increases, the peak overshoot and overshoot width is going to be increases. As Compared to Cu, SWCNT and MWCNT, the peak overshoot and overshoot width for SWCNT is lesser than copper and MWCNT. The MWCNT interconnect is less than that of conventional Copper interconnects.

## REFERENCES

- [1] C. Venkataiah, N. Ramanjaneyulu, Y. Mallikarjuna Rao, V. N. V. Satya Prakash, M. K. Linga Murthy, N. Sreenivasa Rao "Design and performance analysis of buffer inserted on-chip global nano interconnects in VDSM technologies," *Nanotechnology for Environmental Engineering*, May,2022. https://doi.org/10.1007/s41204-022-00249-x

- [2] V. Sulochana, C. Venkataiah, Sunil Agrawal & Balwinder Singh, "Novel Circuit Model of Multi-walled CNT Bundle Interconnects Using Multi-valued Ternary Logic", *IETE Journal of Research*, December 2020. https://doi.org/10.1080/03772063.2020.1864235

- [3] C.Venkataiah, V.N.V. Satya Prakash, K. Mallikarjuna and T. Jayachandra Prasad, "Investigating the effect of chirality, oxide thickness, temperature and channel length variation on a threshold voltage of MOSFET, GNRFET, and CNTFET," *Journal of mechanics of continua and mathematical sciences*, pp 232-244, September 2019. https://doi.org/10.26782/jmcms.spl.3/2019.09.00018.

- [4] Vijay Rao Kumbhare, Punya Prasanna Paltani, C. Venkataiah, and Manoj Kumar Majumder, "Analytical Study of Bundled MWCNT and Edged-MLGNR Interconnects: Impact on Propagation Delay and Area," *IEEE Transactions on Nanotechnology*, vol. 18, pp.606-610, June 2019. https://doi.org/10.1109/TNANO.2019.2920679.

- [5] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Insertion of optimal number of repeaters in pipelined nano interconnects for transient delay minimization," *Circuit systems and signal processing*, February 2019. https://doi.org/10.1007/s00034-018-0876-7

- [6] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "FDTD algorithm to achieve absolute stability in performance analysis of SWCNT interconnects," *Journal of computational electronics*, June 2018. https://doi.org/10.1007/s10825-017-1125-1

- [7] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Crosstalk induced performance analysis of single walled carbon nanotube interconnects using stable finite difference time domain model," *Journal of nanoelectronics and optoelectronics*, vol. 12, pp.1-10, June 2018. https://doi.org/10.1166/jno.2017.2300

- [8] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Signal integrity analysis for coupled SWCNT interconnects using stable recursive algorithm," *Microelectronics Journal*, vol. 74, pp.13-23, April 2018. https://doi.org/10.1016/j.mejo.2018.01.012

- [9] C.V.S. Reddy, C.Venkataiah, V.R.Kumar, S.Maheswaram, N. Jains, S.D. Gupta and S.K. Manhas, "Design and simulation of CNT based nano-transistor for greenhouse gas detection," *Journal of nanoelectronics and optoelectronics*, vol. 12, pp.1-9, April 2018. https://doi.org/10.1166/jno.2017.2133

- [10] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Impact of Supply and Threshold Voltage Scaling on Performance of Cu and CNT Interconnects," *International Journal of Pure and Applied Mathematics*, vol.118, no. 5, pp. 117-126, July 2018.

- [11] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Effect of line parasitic variations on delay and energy of global on-chip VLSI Interconnects in DSM Technology," *International conference on Micro-electronics, Electromagnetics and Telecommunications* (ICMEET), Lecture Notes in Electrical Engineering 434, pp. 221-228, July 2018. https://doi.org/10.1007/978-981-10-4280-5\_23.

- [12] C.Venkataiah, K. Satyaprasad, T. Jayachandra Prasad, "Effect of Interconnect parasitic variations on circuit performance parameters," *IEEE International conference on communication and electronics systems (ICCES)*, Coimbatore, India, pp.289-292, October 2016, 978-1-5090-1066-0/16/\$31.00 ©2016 IEEE

- [13] C. Venkataiah, M. Tejaswi, "A Comparative Study of Interconnect Circuit Techniques for Energy Efficient on-Chip Interconnects," *International Journal of Computer Applications*, vol.109, no. 4, January 2015.

- [14] Manjula jayamma, Y. Mallikarjuna Rao, N. Ramanjaneyulu, Anchula Sathish, "Delay and power efficient technique for VLSI interconnects," *Research and applications: emerging technologies*, vol. 4, Issue 3, HBRP publication, pp.1-7, December 2022. https://doi.org/10.5281/zenodo.7475855

- [15] Manjula jayamma, Y. Mallikarjuna Rao, N. Ramanjaneyulu, Anchula Sathish, "Crosstalk analysis of SLGNR based VLSI interconnects," *Recent trends in analog design and digital devices*, vol. 5, Issue 3, HBRP publication, pp.1-7, December 2022. https://doi.org/10.5281/zenodo.7472762

- [16] Manjula jayamma, Y. Mallikarjuna Rao, N. Ramanjaneyulu, Anchula Sathish, "Delay analysis of VLSI interconnects for high speed applications," *Journal of VLSI Design and signal processing*, vol.8, Issue 3, MAT Journals, pp.23-28, December 2022.

- [17] C. Venkataiah, V. N. V. Satya Prakash, V.Neeraja "Performance Analysis of Boostable Repeater in Different VLSI Interconnects and Applications," *International Journal of Advanced Research in Computer and Communication Engineering*, vol. 3, Issue 11, November 2014.

- [18] C.Venkataiah, C.Vijaya Bharathi, M.Narasimhulu, "Power Efficient Weighted Modulo 2n+1 Adder," International Journal of Computer & Organization Trends, vol.3, Issue 11, Dec 2013.

- [19] K.Venkata Siva Reddy, C.Venkataiah "Design of Adder in Multiple Logic Styles for Low Power VLSI," International Journal of Computer Trends and Technology, vol.3, issue 3, June, 2012.

- [20] Manjula jayamma, N. Ramanjaneyulu, Anchula Sathish, Y. Mallikarjuna Rao, "Analysis of crosstalk in GNR based global interconnects," *Journal of VLSI Design and its Advancement*, vol. 5, Issue 3, HBRP publication, pp.1-8, December 2022. https://doi.org/10.5281/zenodo.7431946

- [21] Manjula jayamma, N. Ramanjaneyulu, Anchula Sathish, Y. Mallikarjuna Rao, "Crosstalk analysis of on-chip VLSI interconnects," *International Journal of Emerging Research in Engineering, Science, and Management*, vol. 1, Issue 4, pp.06-11, Oct-Dec 2022. https://doi.org/10.58482/ijeresm.v1i4.2

- [22] Manjula jayamma, N. Ramanjaneyulu, Anchula Sathish, Y. Mallikarjuna Rao, "Analysis of crosstalk in coupled on-chip VLSI interconnects," *Journal of advancement in communication systems*, vol. 5, issue 3, HBRP publication, pp.1-8, December, 2022. https://doi.org/10.5281/zenodo.7413063